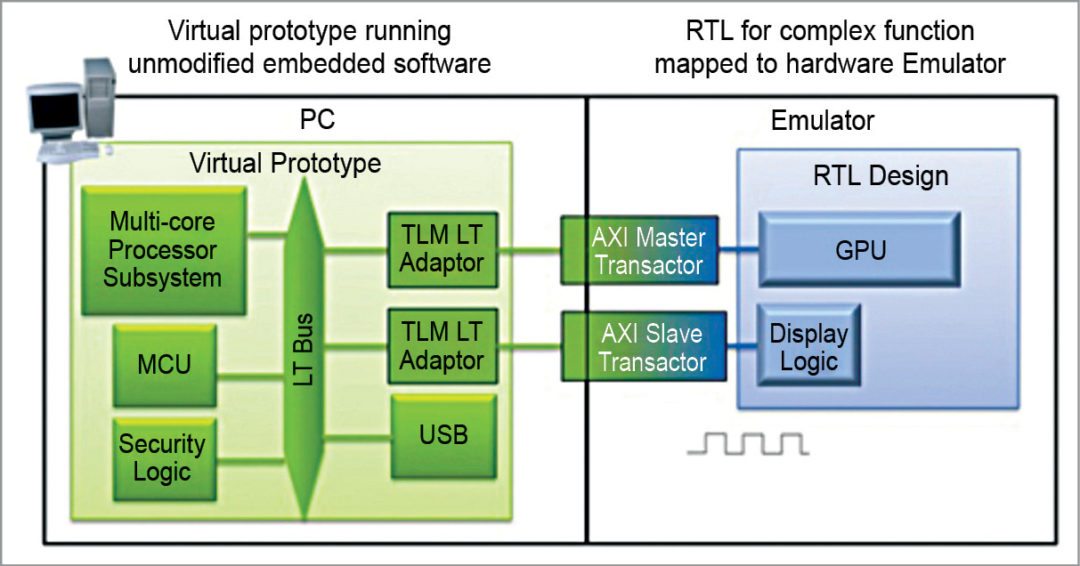

Hybrid emulation is a technique that combines emulation and virtual prototyping to enable earlier architecture optimisation and software development, as well as higher performance for software-driven register-transfer level (RTL) verification even when critical IP RTL is not available. Hybrid emulation is done when part of the system is run in the emulator and the other part is run in a virtual prototype.

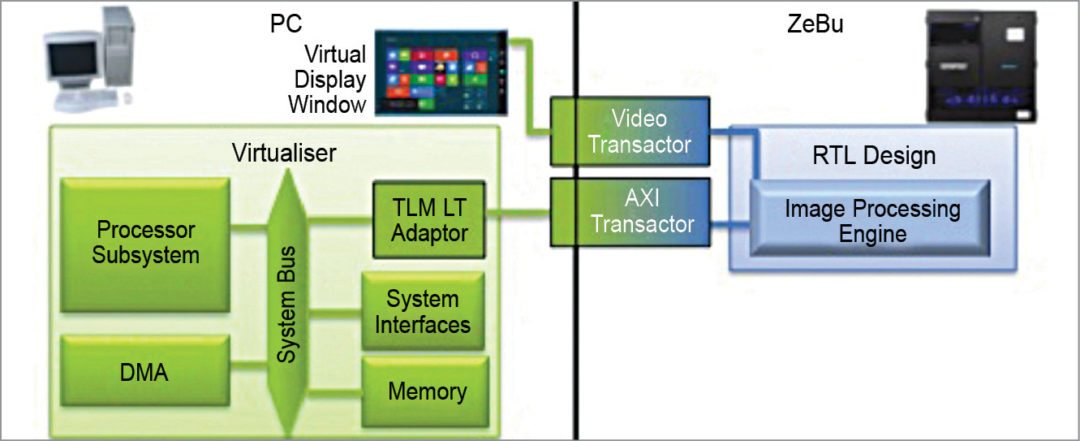

Hybrid emulation with a high-performance emulator can run at multi-megahertz speeds, fast enough to provide a productive debugging experience. When using the hybrid emulation system for software development, you require access to full-visibility debug features of the emulator, where some of the design is modelled. This allows a full system-level view for verification.

Hybrid emulation enables system on chip (SoC) development teams to take full advantage of their investments in a high-performance emulation system across their entire project to better meet increasing software, verification and competitive challenges. Typically, a model of the processor is run in the virtual platform and then the rest of the design is modelled by running the RTL on the emulator.

Benefits of hybrid emulation

Hybrid emulation offers several benefits for SoC architecture, software and verification teams. For architects, it provides a mechanism to implement key elements of the SoC that are only available as RTL in a high-performance, cycle-accurate manner to support their architecture optimisation efforts. Users can choose cycle-accurate, approximately-timed or loosely-timed synchronisation between the virtual prototype and the emulator to make speed/accuracy tradeoffs.

Three main uses for hybrid emulation are architectural validation with accurate models, early software development and hardware verification.

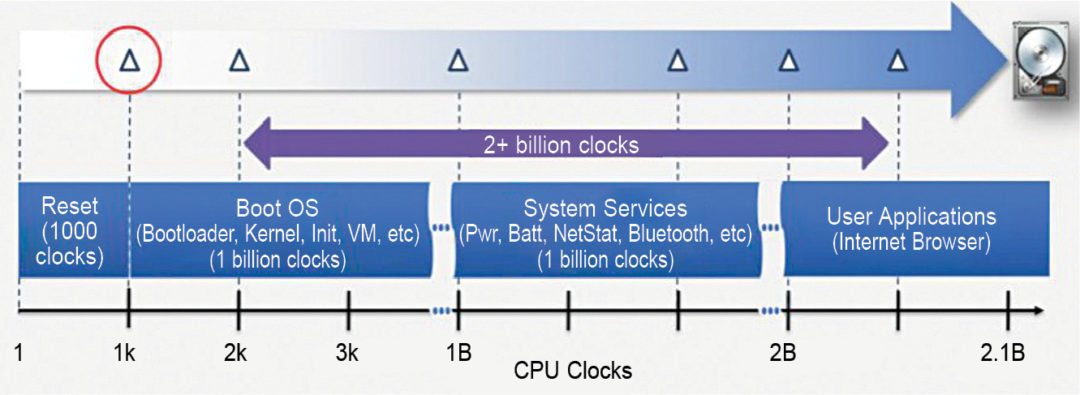

In architectural validation with accurate models, high-speed models used to model processors are only functionally-accurate and not cycle-accurate, and you cannot get accurate performance or accurate performance data from these at that level of detail. Of course, you could just run the RTL of the processor on a simulator, but that is too slow.

In early software development, transactional-level models are often not available, are too low or do not exactly match the RTL for the block. But a hybrid approach with the processor in a virtual platform and all or most of the rest of the design in the emulator is fast enough for productive software development.

Hardware verification allows running actual software load.

Architectural validation.

For SoC architecture validation, you, as a user, have to link a high-performance emulator like ZeBu Server-3 to a virtual prototype exploration tool like Platform Architect MCO. ZeBu Server is the industry’s fastest emulation system. ZeBu solution includes ZeBu Server-3 emulator and a broad portfolio of ZeBu transactors, memory models and ZEMI-3 transactor compiler for rapid development of virtual system-level verification environments.

ZeBu provides the comprehensive debug with full signal visibility and Verdi integration, and supports advanced use modes including power management verification and hybrid emulation with virtual prototypes for architecture optimisation and software development.

Platform Architect MCO enables system designers to explore and optimise the hardware-software partitioning and configuration of the SoC infrastructure, specifically the global interconnect and memory sub-system, to achieve the right system performance, power and cost.

Using a high-performance emulator like ZeBu Server-3 with a virtual prototype exploration tool like Platform Architect MCO, testing typically consists of running application software tests on processor sub-systems in the emulator to drive simulation and monitoring performance. This confirms whether optimised configuration of the architecture design chosen during exploration meets the required performance metrics.

Verdi integration provides the powerful technology that helps comprehend complex and unfamiliar design behaviour, automate difficult and tedious debug processes and unify diverse and complicated design environments. ZeBu Server module emulates 60M gates in nine emulation chips. The components fit better, and fewer design nets get cut. It has less interconnect hardware. Highest performance is two to five megahertz, and it has low power, small size, gets latest processes every two years and is reliable.

Interconnect and memory sub-system peripherals are often modelled in Platform Architect MCO, with cycle-accurate CPU sub-systems modelled in ZeBu Server-3. In ZeBu world, various timing domains maintain their relative clock ratios. Operation in a fully-timed synchronisation mode provides full cycle accuracy. You can use this environment to run a variety of processing loads and data streams, and quickly analyse relative performance tradeoffs between various factors like cache sizes and number of processors. Typical results might show the impact on performance of variations in the number of data streams and processing loads.

Early software development and software-driven verification.

Hybrid emulation enables pre-silicon software development while part of the RTL design is still under development. It is also useful for system-level hardware-software co-verification. Virtual prototypes support the use of instruction-accurate SystemC/C++ processor models and other loosely-timed SystemC TLM-2.0 models. Such models remove the need to wait for silicon to begin developing or validating system software.

The post Hybrid Emulation And The Challenges Ahead appeared first on Electronics For You.

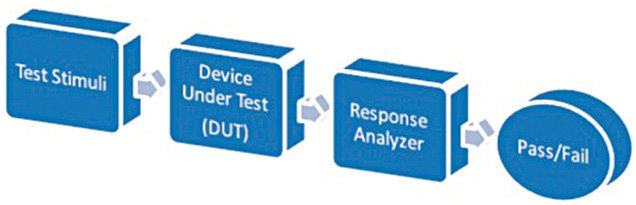

Testing of digital electronic systems generally involves applying a set of test stimuli to inputs of the device-under-test (DUT) and analysing responses of the system using a response analyser. If the DUT generates correct output responses (also called the golden response) for all the input stimuli, the DUT is regarded as fault-free. Those DUTs that fail to meet the golden response are regarded as faulty or defective. Block diagram for testing a device is shown in Fig. 1.

Testing of digital electronic systems generally involves applying a set of test stimuli to inputs of the device-under-test (DUT) and analysing responses of the system using a response analyser. If the DUT generates correct output responses (also called the golden response) for all the input stimuli, the DUT is regarded as fault-free. Those DUTs that fail to meet the golden response are regarded as faulty or defective. Block diagram for testing a device is shown in Fig. 1.

Over 27,000 cyber security incidents were reported in the first six months of this year to Indian Computer Emergency Response Team (CERT-In), Parliament was informed today. These incidents include phishing, website intrusions and defacements as well as ransomware attacks. The government has also formulated Crisis Management Plan for countering cyberattacks and cyber-terrorism for implementation by all ministries/departments of Central government, state government and their organisations and critical sectors.

Over 27,000 cyber security incidents were reported in the first six months of this year to Indian Computer Emergency Response Team (CERT-In), Parliament was informed today. These incidents include phishing, website intrusions and defacements as well as ransomware attacks. The government has also formulated Crisis Management Plan for countering cyberattacks and cyber-terrorism for implementation by all ministries/departments of Central government, state government and their organisations and critical sectors. More than 70 percent of healthcare IT decision makers (ITDMs) believe that traditional security products can secure IoT-Connected medical devices. That’s according to a survey of 200 healthcare ITDMs by IT security company Zingbox, fielded earlier this month.

More than 70 percent of healthcare IT decision makers (ITDMs) believe that traditional security products can secure IoT-Connected medical devices. That’s according to a survey of 200 healthcare ITDMs by IT security company Zingbox, fielded earlier this month. Tens of millions of products ranging from airport surveillance cameras, sensors, networking equipment and IoT devices are vulnerable to a flaw that allows attackers to remotely gain control over devices or crash them.

Tens of millions of products ranging from airport surveillance cameras, sensors, networking equipment and IoT devices are vulnerable to a flaw that allows attackers to remotely gain control over devices or crash them.

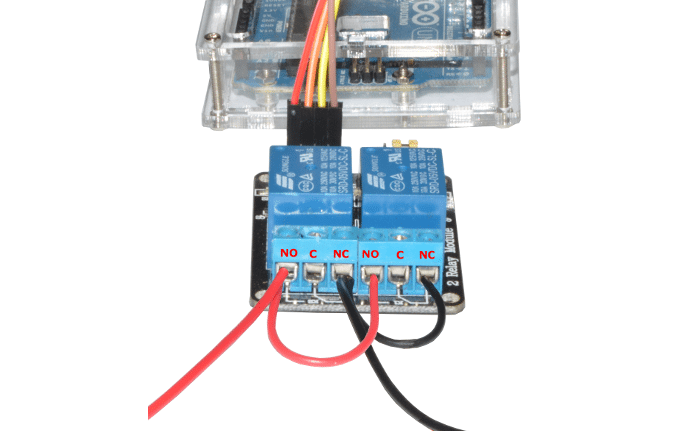

Sometimes there is a need to switch on or off electrical appliances or gadgets after a predetermined time. The circuit presented here can switch on/off any electrical appliance (load) through a relay switch after the specified time set in minutes or seconds.

Sometimes there is a need to switch on or off electrical appliances or gadgets after a predetermined time. The circuit presented here can switch on/off any electrical appliance (load) through a relay switch after the specified time set in minutes or seconds.